# **DUAL Channel 500MSPS DDS with 10-bit DACs**

### **Preliminary Technical Data**

## AD9958

#### **FEATURES**

Two synchronized DDS channels @500 MSPS Independent frequency / phase / amplitude control between all channels Matched latencies for Freq, Phase, and Amplitude changes Excellent channel to channel isolation Frequency sweeping capability Up to 16 levels of modulation (pin selectable) Programmable DAC full scale current Two integrated 10-bit D/A converters(DACs) 32-bit frequency tuning resolution 14-bit phase offset resolution 10-bit output amplitude scaling resolution

Serial I/O Port(SPI) with enhanced data throughput

Software/Hardware controlled power-down Dual supply operation (1.8 V DDS core / 3.3 V serial I/O) Built-in synchronization for multiple devices Selectable REF CLK multipier(PLL) 4x to 20x (bypassable) Selectable REF CLK crystal operation 56 pin LFCSP package

#### **APPLICATIONS**

Agile L.O. frequency synthesis Phased array radar / sonar Instrumentation Synchronized clocking RF source for AOTF

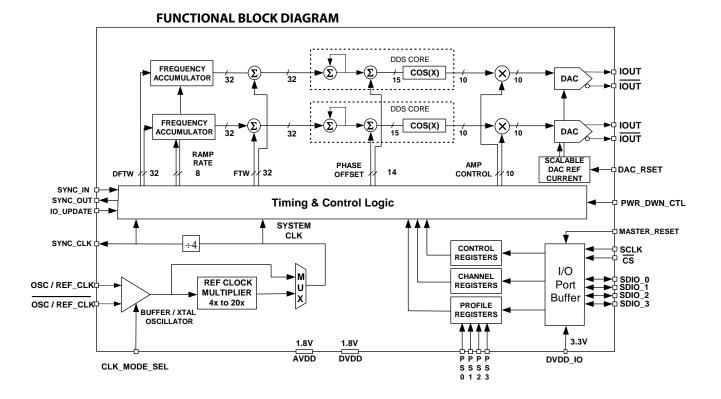

Figure 1 AD9958 Block Diagram

#### Rev. PrB

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.326.8703

© 2004 Analog Devices, Inc. All rights reserved.

### AD9958—SPECIFICATIONS

Table 1. Unless otherwise noted, AVDD, DVDD =  $1.8 V \pm 5\%$ , DVDD\_I/O =  $3.3 V \pm 5\%$ , R<sub>SET</sub> =  $1.96 k\Omega$ , External Reference Clock Frequency = 500 MSPS (REF\_CLK multiplier bypassed)

| Parameter                                                                                                                                                                   | Min           | Тур                      | Мах            | Units                    | Test Conditions/Comments                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------|----------------|--------------------------|-----------------------------------------------------------|

| REF CLOCK INPUT CHARACTERISTICS                                                                                                                                             |               |                          |                |                          | REF_CLK inputs must be AC coupled due to internal biasing |

| Frequency Range                                                                                                                                                             |               |                          |                |                          |                                                           |

| REF_CLK Multiplier bypassed                                                                                                                                                 | 0             |                          | 500            | MHz                      |                                                           |

| REF_CLK Multiplier enabled at 4x(min)                                                                                                                                       | 25            |                          | 125            | MHz                      |                                                           |

| REF_CLK Multiplier enabled at 20x(max)                                                                                                                                      | 5             |                          | 25             | MHz                      |                                                           |

| Internal VCO range w/ REF_CLK multiplier enabled                                                                                                                            | 100           |                          | 500            | MHz                      |                                                           |

| Crystal Ref Clock source mode                                                                                                                                               | 20            |                          | 30             | MHz                      |                                                           |

| Input Power Sensitivity                                                                                                                                                     | -15           |                          | 3              | dBm                      | External 50 ohm termination                               |

| Input voltage level                                                                                                                                                         | 15            | 400                      | 5              | mV                       |                                                           |

| Input Capacitance                                                                                                                                                           |               | 3                        |                | pF                       |                                                           |

| Input Impedance                                                                                                                                                             |               | 1500                     |                | ohms                     |                                                           |

| Duty Cycle w/ REF_CLK Multiplier bypassed                                                                                                                                   |               | 50                       |                | %                        |                                                           |

| Duty Cycle w/ REF_CLK Multiplier enabled                                                                                                                                    | 35            | 50                       | 65             | %                        |                                                           |

| CLK Mode Select logic 1 Voltage                                                                                                                                             | 1.25          |                          | 05             | V                        | Not a 3.3V digital input                                  |

| CLK Mode Select logic 0 Voltage                                                                                                                                             | 1.25          |                          | 0.6            | v                        | Not a 3.3V digital input                                  |

|                                                                                                                                                                             |               |                          | 0.0            | v                        | Must be referenced to AVDD                                |

|                                                                                                                                                                             |               |                          |                |                          | Must be referenced to AVDD                                |

| Resolution                                                                                                                                                                  |               |                          | 10             | Bits                     |                                                           |

| Full Scale Ouput Current                                                                                                                                                    |               | 10                       |                | mA                       |                                                           |

| Gain Error                                                                                                                                                                  | -10           |                          | 10             | %FS                      |                                                           |

| Output Offset                                                                                                                                                               |               |                          | 0.6            | uA                       |                                                           |

| Differential Nonlinearity                                                                                                                                                   | -0.5          |                          | 0.5            | LSB                      |                                                           |

| Integral Nonlinearity                                                                                                                                                       | -1            | _                        | 1              | LSB                      |                                                           |

| Output Capactiance                                                                                                                                                          |               | 5                        |                | pF                       |                                                           |

| Voltage Compliance Range                                                                                                                                                    | AVDD-<br>0.50 |                          | AVDD<br>+ 0.50 | v                        |                                                           |

| Channel to Channel Isolation                                                                                                                                                |               | 60                       |                | dB                       |                                                           |

| Channel to Channel amplitude matching error                                                                                                                                 |               |                          | 2              | %                        |                                                           |

| WIDEBAND SFDR                                                                                                                                                               |               |                          |                |                          | Wideband SFDR defined as DC t<br>Nyquist                  |

| 1-20 MHz Analog Out                                                                                                                                                         |               | -65                      |                | dBc                      |                                                           |

| 20-60 MHz Analog Out                                                                                                                                                        |               | -62                      |                | dBc                      |                                                           |

| 60-100 MHz Analog Out                                                                                                                                                       |               | -59                      |                | dBc                      |                                                           |

| 100-150 MHz Analog Out                                                                                                                                                      |               | -56                      |                | dBc                      |                                                           |

| 150-200 MHz Analog Out                                                                                                                                                      |               | -54                      |                | dBc                      |                                                           |

| NARROWBAND SFDR                                                                                                                                                             |               |                          |                |                          |                                                           |

| 1.1 MHz Analog Out (+/- 10kHz)                                                                                                                                              |               | -90                      |                | dBc                      |                                                           |

| 1.1 MHz Analog Out (+/- 50kHz)                                                                                                                                              |               | -88                      |                | dBc                      |                                                           |

| 1,1 MHz Analog Out (+/- 250kHz)                                                                                                                                             |               | -86                      |                | dBc                      |                                                           |

| 1.1 MHz Analog Out (+/- 1MHz)                                                                                                                                               |               | -85                      |                | dBc                      |                                                           |

|                                                                                                                                                                             |               |                          | 1              |                          |                                                           |

| -                                                                                                                                                                           |               | -90                      |                | dBc                      |                                                           |

| 15.1 MHz Analog Out (+/- 10kHz)                                                                                                                                             |               | -90<br>-87               |                | dBc<br>dBc               |                                                           |

| 15.1 MHz Analog Out (+/- 10kHz)<br>15.1 MHz Analog Out (+/- 50kHz)                                                                                                          |               | -87                      |                | dBc                      |                                                           |

| 15.1 MHz Analog Out (+/- 10kHz)                                                                                                                                             |               |                          |                |                          |                                                           |

| 15.1 MHz Analog Out (+/- 10kHz)<br>15.1 MHz Analog Out (+/- 50kHz)<br>15.1 MHz Analog Out (+/- 250kHz)<br>15.1 MHz Analog Out (+/- 1MHz)                                    |               | -87<br>-85<br>-83        |                | dBc<br>dBc<br>dBc        |                                                           |

| 15.1 MHz Analog Out (+/- 10kHz)<br>15.1 MHz Analog Out (+/- 50kHz)<br>15.1 MHz Analog Out (+/- 250kHz)<br>15.1 MHz Analog Out (+/- 1MHz)<br>40.1 MHz Analog Out (+/- 10kHz) |               | -87<br>-85<br>-83<br>-90 |                | dBc<br>dBc<br>dBc<br>dBc |                                                           |

| 15.1 MHz Analog Out (+/- 10kHz)<br>15.1 MHz Analog Out (+/- 50kHz)<br>15.1 MHz Analog Out (+/- 250kHz)<br>15.1 MHz Analog Out (+/- 1MHz)                                    |               | -87<br>-85<br>-83        |                | dBc<br>dBc<br>dBc        |                                                           |

# Preliminary Technical Data

## AD9958

| Parameter                                             | Min | Тур        | Max | Units              | <b>Test Conditions/Comments</b> |

|-------------------------------------------------------|-----|------------|-----|--------------------|---------------------------------|

| 75.1 MHz Analog Out (+/- 10kHz)                       |     | -87        |     | dBc                |                                 |

| 75.1 MHz Analog Out (+/- 50kHz)                       |     | -85        |     | dBc                |                                 |

| 75.1 MHz Analog Out (+/- 250kHz)                      |     | -83        |     | dBc                |                                 |

| 75.1 MHz Analog Out (+/- 1MHz)                        |     | -82        |     | dBc                |                                 |

| 100.1 MHz Analog Out (+/- 10kHz)                      |     | -87        |     | dBc                |                                 |

| 100.1 MHz Analog Out (+/- 50kHz)                      |     | -85        |     | dBc                |                                 |

| 100.1 MHz Analog Out (+/- 250kHz)                     |     | -83        |     | dBc                |                                 |

| 100.1 MHz Analog Out (+/- 1MHz)                       |     | -81        |     | dBc                |                                 |

| 200.1 MHz Analog Out (+/- 10kHz)                      |     | -87        |     | dBc                |                                 |

| 200.1 MHz Analog Out (+/- 50kHz)                      |     | -85        |     | dBc                |                                 |

| 200.1 MHz Analog Out (+/- 250kHz)                     |     | -83        |     | dBc                |                                 |

| 200.1 MHz Analog Out (+/- 1MHz)                       |     | -81        |     | dBc                |                                 |

| PHASE NOISE CHARACTERISTICS                           |     |            |     |                    |                                 |

| Residual Phase Noise @15.1 MHz(Aout)                  |     | TOD        |     | -ID - (   I -      |                                 |

| @1kHz_offset                                          |     | TBD        |     | dBc/ Hz            |                                 |

| @10kHz offset                                         |     | TBD        |     | dBc/ Hz            |                                 |

| @100kHz offset                                        |     | TBD        |     | dBc/ Hz            |                                 |

| @1MHz offset                                          |     | TBD        |     | dBc/ Hz            |                                 |

| Residual Phase Noise @ 75.1 MHz(Aout)<br>@1kHz offset |     | TBD        |     | dBc/ Hz            |                                 |

| @10kHz_offset                                         |     | TBD        |     | dBc/ Hz            |                                 |

| @10kHz offset                                         |     | TBD        |     | dBc/ Hz            |                                 |

| @100kH2 offset                                        |     | TBD        |     | dBc/ Hz            |                                 |

| Residual Phase Noise @ 200.1 MHz(Aout)                |     | TUU        |     | UDC/ 112           |                                 |

| @1kHz_offset                                          |     | TBD        |     | dBc/ Hz            |                                 |

| @10kHz_offset                                         |     | TBD        |     | dBc/ Hz            |                                 |

| @100kHz offset                                        |     | TBD        |     | dBc/ Hz            |                                 |

| @1MHz offset                                          |     | TBD        |     | dBc/ Hz            |                                 |

| Residual Phase Noise @ 15.1 MHz(Aout)                 |     |            |     |                    |                                 |

| w/ REF_CLK multiplier enabled 4x                      |     |            |     |                    |                                 |

| @1kHz_offset                                          |     | TBD        |     | dBc/ Hz            |                                 |

| @10kHz_offset                                         |     | TBD        |     | dBc/ Hz            |                                 |

| @100kHz offset                                        |     | TBD        |     | dBc/ Hz            |                                 |

| @1MHz offset                                          |     | TBD        |     | dBc/ Hz            |                                 |

| Residual Phase Noise @ 75.1 MHz(Aout)                 |     |            |     |                    |                                 |

| w/ REF_CLK multiplier enabled 4x                      |     | TOO        |     | 15 (11             |                                 |

| @1kHz offset<br>@10kHz offset                         |     | TBD        |     | dBc/ Hz<br>dBc/ Hz |                                 |

| @10kHz offset                                         |     | TBD<br>TBD |     | dBc/ Hz<br>dBc/ Hz |                                 |

| @100kH2 offset                                        |     | TBD        |     | dBc/ Hz            |                                 |

| Residual Phase Noise @ 200.1 MHz(Aout)                |     | IDU        |     |                    |                                 |

| w/ REF_CLK multiplier enabled 4x                      |     |            |     |                    |                                 |

| @1kHz_offset                                          |     | TBD        |     | dBc/ Hz            |                                 |

| -                                                     |     |            |     |                    |                                 |

| @10kHz offset                                         |     | TBD        |     | dBc/ Hz            |                                 |

| @100kHz offset                                        |     | TBD        |     | dBc/ Hz            |                                 |

| @1MHz offset                                          |     | TBD        |     | dBc/ Hz            |                                 |

| SERIAL PORT TIMING CHARACTERISTICS                    |     |            |     |                    |                                 |

| Maximum Frequency                                     |     | 200        |     | MHz                |                                 |

| Minimum Clock Pulsewidth Low (t <sub>PWL</sub> )      |     | TBD        |     | ns                 |                                 |

| ······································                | 1   | 1          | 1   | 1                  |                                 |

## AD9958

# Preliminary Technical Data

| Maximum Clock Rise/Fall Time                                                   | 1   | TBD |     | ns       |                                                                                           |

|--------------------------------------------------------------------------------|-----|-----|-----|----------|-------------------------------------------------------------------------------------------|

| Minimum Data Setup Time (t <sub>DS</sub> )                                     |     | TBD |     | ns       |                                                                                           |

| Minimum Data Hold Time                                                         |     | TBD |     | ns       |                                                                                           |

| MISC TIMING CHARACTERISTICS                                                    |     |     |     |          |                                                                                           |

| Master_Reset minimum Pulsewidth                                                |     | TBD |     | Sync CLK |                                                                                           |

| I/O_Update minimum Pulsewidth                                                  |     | 1   |     | Sync CLK |                                                                                           |

| Minimum setup time (IO_Update to Sync_CLK)                                     |     | TBD |     | ns       | Rising edge to rising edge                                                                |

| Minimum hold time (IO_Update to Sync_CLK)                                      |     | 0   |     | ns       | Rising edge to rising edge                                                                |

| Minimum setup time (Profile inputs to Sync_CLK)                                |     | TBD |     | ns       |                                                                                           |

| Minimum hold time (Profile inputs to Sync_CLK)                                 |     | 0   |     | ns       |                                                                                           |

| DATA LATENCY (PIPE LINE DELAY)                                                 |     |     |     |          | Pipeline delays for Freq, Phase,<br>Amp changes are programmable to<br>match one another. |

| Matched pipe line of Freq, Phase, Amplitude                                    |     | TBD |     | Sys Clks | matched                                                                                   |

| Frequency word to DAC output                                                   |     | TBD |     | Sys Clks | unmatched                                                                                 |

| Phase Offset word to DAC output                                                |     | TBD |     | Sys Clks | unmatched                                                                                 |

| Amplitude word to DAC output                                                   |     | TBD |     | Sys Clks | unmatched                                                                                 |

| CMOS LOGIC INPUTS                                                              |     |     |     |          |                                                                                           |

| V <sub>IH</sub>                                                                | 2.2 |     |     | v        |                                                                                           |

| VIL                                                                            |     |     | 0.6 | V        |                                                                                           |

| Logic 1 Current                                                                |     | 3   | 12  | uA       |                                                                                           |

| Logic 0 Current                                                                | -12 |     |     | uA       |                                                                                           |

| Input Capacitance                                                              |     | 2   |     | pF       |                                                                                           |

| CMOS LOGIC OUTPUTS (1 mA Load)                                                 |     |     |     |          |                                                                                           |

| V <sub>OH</sub>                                                                | 2.8 |     |     | V        |                                                                                           |

| Vol                                                                            |     |     | 0.4 | V        |                                                                                           |

| POWER SUPPLY                                                                   |     |     |     |          |                                                                                           |

| Total Power Dissipation- all channels ON, single-tone mode                     |     | TBD |     | mW       |                                                                                           |

| Maximum Power Dissipation- all channels, freq accumulator output multiplier ON |     | TBD |     |          |                                                                                           |

| lavdd – All Channels ON, Single tone mode                                      |     | TBD |     | mA       |                                                                                           |

| lavdd – All Ch(s) ON, Freq accum, and output multiplier ON                     |     | TBD |     | mA       |                                                                                           |

| ldvdd – All Ch(s) ON, Single tone mode                                         |     | TBD |     | mA       |                                                                                           |

| Idvdd – All Ch(s) ON, Freq accum, and output multiplier ON                     |     | TBD |     | mA       |                                                                                           |

| ldvdd_l/O                                                                      |     | TBD |     | mA       |                                                                                           |

| Power down Mode                                                                |     | TBD |     | mA       |                                                                                           |

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                                | Rating          |

|------------------------------------------|-----------------|

| Maximum Junction Temperature             | 150°C           |

| DVDD_I/O (Pin 49)                        | 4 V             |

| AVDD, DVDD                               | 2 V             |

| Digital Input Voltage (DVDD_I/O = 3.3 V) | –0.7 V to +4V   |

| Digital Output Current                   | 5 mA            |

| Storage Temperature                      | –65°C to +150°C |

| Operating Temperature                    | –40°C to +105°C |

| Lead Temperature (10 sec Soldering)      | 300°C           |

| ALθ                                      | 21°C/W          |

| θ」ϲ                                      | 2°C/W           |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

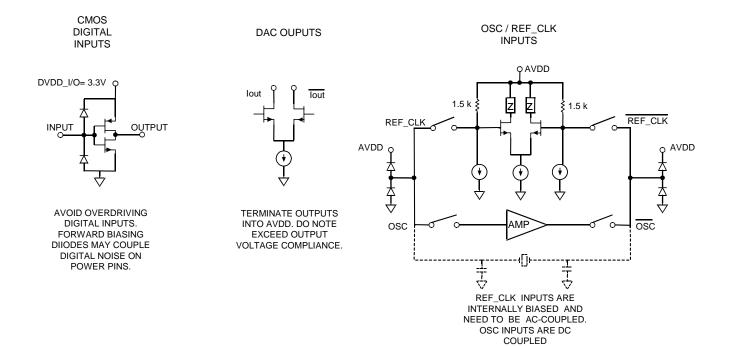

Figure 1 Equivalent input and output circuits

#### **PRODUCT OVERVIEW**

The AD9958 consists of two independently programmable DDS channels. Since both channels share a common system clock, they are inherently synchronized. If more than two channels are required, synchronizing multiple AD9958s is a simple task. The AD9958 features independent frequency, phase, and amplitude control of each channel; this allows for the correction of imbalances due to analog processing such as filtering, amplification, or PCB layout related mismatches. The AD9958 supports frequency sweeping for radar and instrumentation applications.

The AD9958 uses advanced DDS technology which provides low power dissipation with high performance. The device incorporates two integrated high speed 10-bit DAC with excellent wideband and narrowband SFDR. Each DDS has a 32bit frequency tuning word, 14-bits of phase offset, and a 10-bit output scale multiplier.

Each DAC has it own programmable reference to enable a different full scale current for each channel.

Each DDS acts as a high resolution frequency divider with the REF\_CLK as the input and the DAC providing the output. The REF\_CLK input source is common to both DDS channels, and can be driven directly, or used in combination with an integrated REF\_CLK multiplier (using a PLL) up to a maximum of 500 MSPS. The REF\_CLK multiplication factor is programmable from 4 to 20, in integer steps. The REF\_CLK input features an oscillator which supports either a crystal as a source, or may be bypassed. The crystal frequency must be between 20MHz and 30MHz. The crystal can be used with or without the REF\_CLK multiplier.

The DAC outputs are supply referenced and must be terminated into AVDD by a resistor, or an AVDD center-tapped transformer.

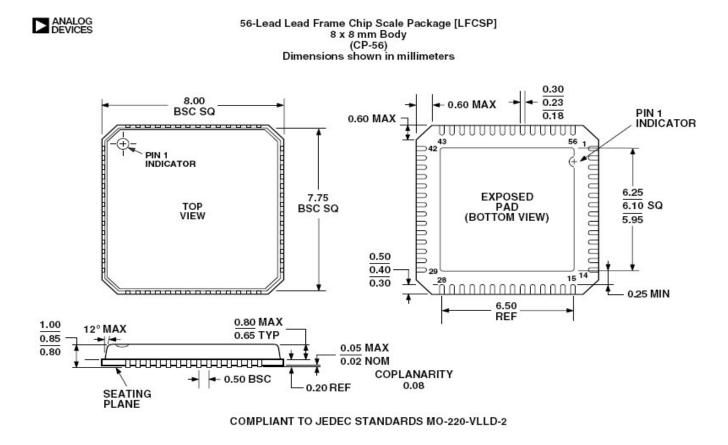

The AD9958 comes in a space-saving 56-lead LFCSP package. The DDS core (AVDD and DVDD pins) must be powered by a 1.8V supply. The digital I/O interface (SPI) operates at 3.3V and requires that the pin labeled "DVDD\_I/O" (pin 49) be connected to 3.3V.

The AD9958 operates over the extended industrial temperature range of -40C to +85  $\,$

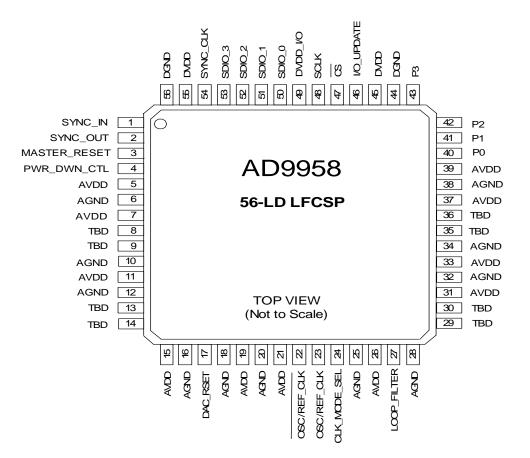

## PIN CONFIGURATION

- Notes 1) The exposed EPAD on bottom side of package is an electrical connection and must be soldered to ground.

- 2) Pin 49 is DVDD\_IO and is tied to 3.3V.

### Table 3. Pin Function Descriptions

| Pin No.           | Mnemonic             | I/O | Description                                                                                                                                                                                                                    |

|-------------------|----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | SYNC_IN              | Ι   | Used to synchronize multiple AD9959s. Connect to the SYNC_OUT pin of the master AD9959.                                                                                                                                        |

| 2                 | SYNC_OUT             | 0   | Used to synchronize multiple AD9959s. Connect to the SYNC_IN pin of the slave AD9959.                                                                                                                                          |

| 3                 |                      | Т   | Active high reset pin. Asserting the RESET pin forces the AD9959's internal registers to their                                                                                                                                 |

|                   | MASTER_RESET         |     | default state, as described in the serial I/O port register map section in this document.                                                                                                                                      |

| 4                 | PWR_DWN_CTL          | Т   | External Power-Down Control.                                                                                                                                                                                                   |

| 5,7,11,15,19,21,  | AVDD                 | Т   | Analog Power Supply Pins (1.8V).                                                                                                                                                                                               |

| 26,31,33,37,39    |                      |     |                                                                                                                                                                                                                                |

| 6,10,12,16,18,20, | AGND                 | I.  | Analog Ground Pins.                                                                                                                                                                                                            |

| 25,28,32,34,38    |                      |     |                                                                                                                                                                                                                                |

| 45, 55            | DVDD                 | I.  | Digital Power Supply Pins (1.8 V).                                                                                                                                                                                             |

| 44, 56            | DGND                 | I   | Digital Power Ground Pins.                                                                                                                                                                                                     |

| 8                 | TBD                  |     |                                                                                                                                                                                                                                |

| 9                 | TBD                  |     | These pins are still being evaluated for DAC outputs for                                                                                                                                                                       |

| 13                | TBD                  |     | Channels 0 and 1.                                                                                                                                                                                                              |

| 14                | TBD                  |     |                                                                                                                                                                                                                                |

| 17                | DAC_R <sub>SET</sub> | I   | Establishes the reference current for all DACs. A 1.962 k $\Omega$ resistor (nominal) is connected from pin 17 to AGND.                                                                                                        |

| 22                | OSC / REF_CLK        | I   | Complementary Reference Clock/Oscillator Input. When the REF_CLK is operated in single-<br>ended mode, this pin should be decoupled to AVDD or AGND with a 0.1 µF capacitor.                                                   |

| 23                | OSC / REF_CLK        | I   | Reference Clock/Oscillator Input. When the REF_CLK is operated in single-ended mode, this is the input.                                                                                                                        |

| 24                | CLK_MODE_SEL         | I   | Control Pin for the Oscillator Section. When high (1.8V), the oscillator section is enabled to accept a crystal as the REFCLK source. When low, the oscillator section is bypassed.                                            |

|                   |                      |     | CAUTION: Do not drive this pin beyond 1.8V.                                                                                                                                                                                    |

| 27                | LOOP_FILTER          | I   | Connect to the external zero compensation network of the PLL loop filter for the REFCLK multiplier. For a 20x multiplier value the network should be a $1.2k\Omega$ resistor in series with a $1.2$ nF capacitor tied to AVDD. |

| 29                | TBD                  |     |                                                                                                                                                                                                                                |

| 30                | TBD                  |     | These pins are still being evaluated for DAC outputs for                                                                                                                                                                       |

| 35                | TBD                  |     | Channels 0 and 1.                                                                                                                                                                                                              |

| 36                | TBD                  |     |                                                                                                                                                                                                                                |

| 40, 41,           | PS0, PS1,            | Т   | These Pins are synchronous to the SYNC_CLK (pin 54). Any change in Profile inputs transfers                                                                                                                                    |

| 42, 43            | PS2, PS3             |     | the contents of the internal buffer memory to the I/O active registers (same as an external I/O _UPDATE).                                                                                                                      |

| 46                | I/O_UPDATE           | I.  | A rising edge detected on this pin transfers data from serial port buffer to active registers.                                                                                                                                 |

| 47                | CS                   | I.  | Active low chip select allowing multiple devices to share a common I/O bus (SPI).                                                                                                                                              |

| 48                | SCLK                 | I   | Serial data clock for I/O operations. Data bits are written on rising edge of SCLK and read on the falling edge of SCLK.                                                                                                       |

| 49                | DVDD_I/O             | Т   | 3.3 V Digital Power Supply for SPI port and I/O (excluding CLK_MODE_SEL).                                                                                                                                                      |

| 50, 51            | SDIO_0, SDIO_1       | I/O | These data pins have multiple functions. Data I/O pins for the serial I/O port operation. They                                                                                                                                 |

| 52, 53            | SDIO_2, SDIO_3       |     | are also used as data pins in modulation modes.                                                                                                                                                                                |

| 54                | SYNC_CLK             | 0   | I/O_UPDATE and Profile signals should meet the set-up and hold requirements with respect to this signal in order to guarantee a fixed pipeline delay of data to DAC outputs.                                                   |

## **Preliminary Technical Data**

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.